|

Тема 25. Лічильники.

25.1. Загальні поняття.

Лічильники представляють більш високий рівень складності цифрових мікросхем, ніж регістри, що мають внутрішню пам'ять. Хоча в основі будь-якого лічильника лежать ті ж самі трігери, які утворюють і регістри, але в лічильниках трігери сполучені складнішими зв'язками, внаслідок чого їх функції складніші, і на їх основі можна будувати складніші пристрої, ніж на регістрах. Так само, як і у разі регістрів, внутрішня пам'ять лічильників — оперативна, тобто її вміст зберігається тільки до тих пір, поки включено живлення схеми. З виключенням живлення пам'ять стирається, а при новому включенні живлення схеми вміст пам'яті буде довільним, випадковим, залежним тільки від конкретної мікросхеми, тобто вихідні сигнали лічильників будуть довільними.

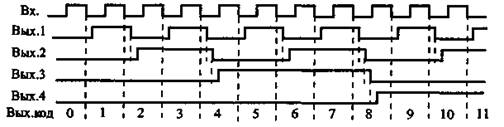

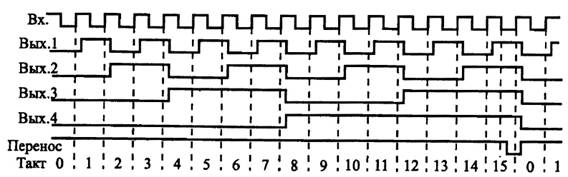

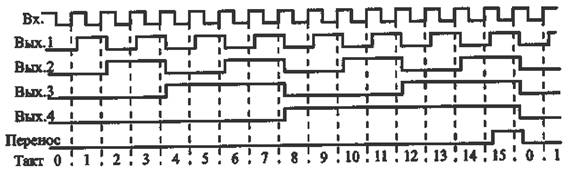

Малюнок 25. 1. Робота 4-розрядного двійкового лічильника.

Як випливає з самої назви, лічильники призначені для підрахунку вхідних імпульсів. Тобто з приходом кожного нового вхідного імпульсу двійковий код на виході лічильника збільшується (або зменшується) на одиницю (Малюнок 25.1). Спрацьовувати лічильник може по негативному фронту вхідного (тактового) сигналу (як на малюнку) або по позитивному фронту вхідного сигналу. Режим підрахунку забезпечується використовуванням внутрішніх трігерів, що працюють в рахунковому режимі. Виходи лічильника є якраз виходами цих трігерів. Кожний вихід лічильника є розрядом двійкового коду, причому розряд, що змінюється частіше за інші (по кожному вхідному імпульсу), буде молодшим, а розряд, що змінюється рідше за інші — старшим.

Лічильник може працювати на збільшення вихідного коду по кожному вхідному імпульсу, це основний режим, що є у всіх лічильниках, він називається режимом прямого підрахунку. Лічильник може також працювати на зменшення вихідного коду по кожному вхідному імпульсу, це режим зворотного або інверсного підрахунку, передбачений в лічильниках, званих реверсивними. Інверсний рахунок буває досить зручний в схемах, де необхідно порахувати задану кількість вхідних імпульсів.

Більшість лічильників працює в звичайному двійковому коді, тобто рахує від 0 до (2N — 1), де N — число розрядів вихідного коду лічильника. Наприклад, 4-розрядний лічильник в режимі прямого підрахунку рахуватиме від 0 (код 0000) до 15 (код 1111), а 8-розрядний — від 0 (код 0000 0000) до 255 (код 1111 1111). Після максимального значення коду лічильник по наступному вхідному імпульсу змінюється знову на 0, тобто працює по колу. Якщо ж рахунок інверсний, то лічильник рахує до нуля, а далі переходить до максимального коду 111... 1.

Є також двійково-десяткові лічильники, кінцевий код на виході яких не перевищує максимального двійково-десяткового числа, можливого при даній кількості розрядів. Наприклад, 4-розрядний двійково-десятковий лічильник в режимі прямого підрахунку буде рахувати від 0 (код 0000) до 9 (код 1001), а потім знову від 0 до 9. А 8-розрядний двійково-десятковий лічильник буде рахувати від 0 (код 0000 0000) до 99 (код 1001 1001). При інверсному підрахунку двійково-десяткові лічильники рахують до нуля, а з наступним вхідним імпульсом переходять до максимально можливого двійково-десяткового числа (тобто 9 для 4-розрядного лічильника, 99 для 8-розрядного лічильника). Двійково-десяткові лічильники зручні, наприклад, при організації десяткової індикації їх вихідного коду. Застосовуються вони набагато рідше за звичайні двійкові лічильники.

По швидкодії всі лічильники діляться на три великі групи:

- асинхронні (або послідовні) лічильники;

- синхронні лічильники з асинхронним перенесенням (або паралельні лічильники з послідовним перенесенням);

- синхронні (або паралельні) лічильники.

Принципові відмінності між цими групами виявляються тільки на другому рівні представлення, на рівні моделі з тимчасовими затримками. Найбільшою швидкодією володіють синхронні лічильники, а найменшою — асинхронні лічильники, найбільш просто керовані серед інших. Кожна група лічильників має свої області використання, на яких ми і зупинимося.

25.2. Асинхронні лічильники

Асинхронні лічильники будуються з простого ланцюжка JK-трігерів, кожний з яких працює в рахунковому режимі. Вихідний сигнал кожного трігера служить вхідним сигналом для наступного трігера. Тому всі розряди (виходи) асинхронного лічильника перемикаються послідовно (звідси назва — послідовні лічильники), один за іншим, починаючи з молодшого і кінчаючи старшим. Кожний наступний розряд перемикається із затримкою щодо попереднього (Малюнок 25.2), тобто, не одночасно з вхідним сигналом і з іншими розрядами.

Малюнок 25.2. Тимчасова діаграма роботи 4-розрядного асинхронного лічильника.

Чим більше розрядів має лічильник, тим більший час йому потрібен на повне перемикання всіх розрядів. Затримка перемикання кожного розряду приблизно рівна затримці трігера, а повна затримка встановлення коду на виході лічильника рівна затримці одного розряду, помноженій на число розрядів лічильника. Легко помітити, що при періоді вхідного сигналу, меншому ніж повна затримка встановлення коду лічильника, правильний код на виході лічильника просто не встигне встановитися, тому така ситуація не має сенсу. Це створює обмеження на період (частоту) вхідного сигналу, причому збільшення, наприклад, удвічі кількості розрядів лічильника автоматично зменшує удвічі гранично допустиму частоту вхідного сигналу.

Таким чином, якщо нам потрібен вихідний код асинхронного лічильника, тобто всі його вихідні сигнали (розряди) одночасно, то повинна виконуватися наступна нерівність:

Т > Nt3

де Т — період вхідного сигналу, N — число розрядів лічильника, t3 — час затримки одного розряду.

Треба ще врахувати, що за періодом вхідного сигналу повинен встигнути спрацювати пристрій (вузол), на який поступає вихідний код лічильника, інакше лічильник просто не потрібен, тому обмеження на частоту вхідного сигналу звичайно буває ще жорсткіше.

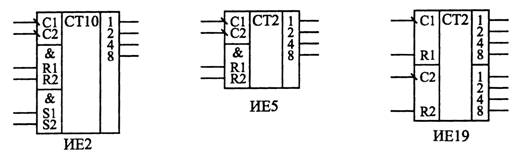

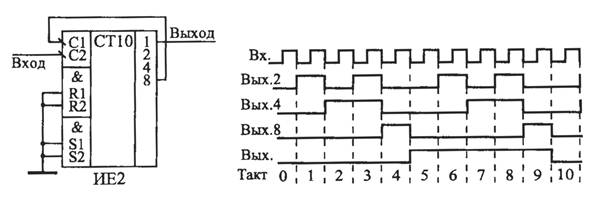

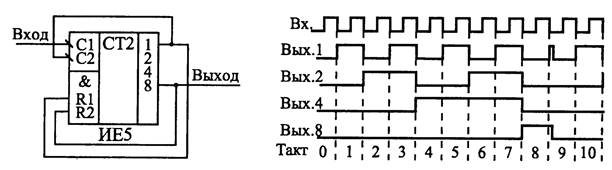

У складі стандартних серій цифрових мікросхем асинхронних лічильників є небагато. Як приклад на малюнку 25.3. приведені три з них: чотирьохрозрядний двійково-десятковий лічильник ИЕ2, чотирьохрозрядний двійковий лічильник ИЕ5 і восьмирозрядний двійковий лічильник ИЕ19 (він є двійковиий чотирьохрозрядний лічильник).

Малюнок 25.3. Асинхронні лічильники стандартних серій.

Управління роботою всіх цих лічильників дуже просте: є лише входи скидання на нуль або входи установки в 9 (тільки в ИЕ2). Всі асинхронні лічильники працюють по нижньому фронту вхідного сигналу С. У всіх трьох лічильників виділено дві незалежні частини, що збільшує сферу їх використання. При об'єднанні цих двох частин виходить лічильник максимальної розрядності. Виходи лічильників позначають на схемах 0, 1,2, 3 ... (як номери розрядів вихідного двійкового коду) або 1, 2, 4, 8 ... (як вага кожного розрядудвійкового коду).

Лічильник ИЕ2 має дві частини: один трігер (вхід С1, вихід 1) і три трігери (вхід С2 і виходи 2, 4, 8). Таким чином, він складається з однорозрядного лічильника і трьохрозрядного лічильника. Одиночний трігер працює в звичайному рахунковому режимі, змінюючи свій стан по кожному нижньому фронту сигналу С1, тобто ділить частоту вхідного сигналу на 2. Три трігери, що залишилися, включені так, щоб рахувати до 5, тобто ділити вхідну частоту сигналу С2 на 5. Після досягнення коду 4 (тобто 100) на виходах 2, 4 і 8 цей трьохрозрядний лічильник по наступному нижньому фронту сигналу С2 скидається в нуль. В результаті об'єднання виходу 1 мікросхеми з входом С2 ми одержуємо 4-розрядний двійково-десятковий лічильник, що ділить частоту вхідного сигналу С1 на 10, що скидається в нуль після досягнення на виходах 1, 2, 4, 8 коду 9 (тобто 1001) по негативному фронту сигналу С1.

Лічильник ИЕ2 має два входи асинхронного скидання в нуль R1 і R2, з'єднані по функції І, а також два входи установки в 9 — S1 і S2, також з'єднаних по функції І, причому установка в 9 блокує установку в нуль. Наявність цих входів скидання і установки дозволяє будувати на базі лічильника ИЕ2 дільники частоти з різними коефіцієнтами розподілу. Правда, цей лічильник використовується досить рідко, значно рідше, ніж інші асинхронні лічильники ИЕ5 і ИЕ19.

Таблиця істинності асинхронного лічильника ИЕ2 при сполученому виході 1 і вході С2 (при 4-розрядному вихідному коді) приведена нижче (таблиця 25.1), а стан виходів за рахунку вхідних імпульсів по тактах представлені в таблиці 25.2.

Лічильник ИЕ5 так само, як і ИЕ2, має дві частини: один трігер (однорозрядний лічильник) з входом С1 і виходом 1 і три трігери (трьохрозрядний лічильник) з входом С2 і виходами 2, 4, 8. Обидва лічильники двійкові, тобто перший рахує до двох, а другий — до 8. При об'єднанні входу С2 з виходом 1 виходить 4-розрядний двійковий лічильник, що рахує до 16. Рахунок проводиться по негативному фронту вхідних сигналів С1 і С2. Передбачена можливість скидання лічильника на нуль по сигналах R1 і R2, з'єднаних по функції І.

Таблиця істинності лічильника ИЕ5 при з'єднанні входу С2 і входу 1 (при 4-розрядному вихідному коді) приведена нижче (таблиця 25.3.).

Малюнок 25.4. Об'єднання трьох лічильників ИЕ5 для збільшення розрядності

Об'єднувати лічильники ИЕ5 для збільшення розрядності дуже просто: вихід 8 попереднього лічильника (видаючого більш молодші розряди) потрібно з'єднати з входом С1 наступного лічильника (видаючого більш старші розряди). На малюнку 25.4 показано з'єднання трьох лічильників ИЕ5 для одержання 12-розрядного асинхронного лічильника з скиданням на нуль. Так само можна об'єднувати і лічильники ИЕ2, додаючи при цьому входи загальної установки лічильника в код 99...9. Проте при об'єднанні треба пам'ятати, що додавання кожного нового розряду збільшує загальну затримку перемикання одержаного лічильника. Багаторозрядний асинхронний лічильник може вийти неприйнятно повільним.

Лічильник ИЕ19 можна вважати здвоєним варіантом лічильника ИЕ5. Він включає в себе два ідентичних незалежних один від одного 4-розрядних асинхронних лічильника, кожний з яких має свій рахунковий вхід С і свій вхід скидання R. Рахують обидва лічильники імпульси, що входять в мікросхему, по негативному фронту на своїх входах С1 і С2. Скидаються вони одиничними сигналами на своїх входах скидання R1 і R2.

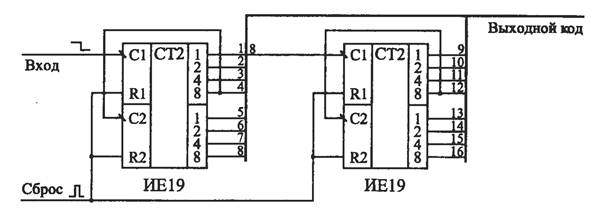

Лічильники, що входять в мікросхему ИЕ19, можна використовувати по одному, але можна і об'єднати їх для отримання 8-розрядного асинхронного лічильника з виходами 1,2, 4, 8, 16, 32, 64, 128. Для такого об'єднання достатньо з'єднати вихід 8 першого лічильника з рахунковим входом С2 другого лічильника. Якщо з'єднати два лічильники ИЕ19 (Малюнок 25.5), то вийде вже 16-розрядний асинхронний двійковий лічильник. При цьому вихід 8 другого лічильника з'єднується з рахунковим входом С1 першого лічильника. Проте і в даному випадку кожний наступний розряд перемикається із затримкою після перемикання попереднього.

Малюнок 25.5. Об'єднання двох лічильників ИЕ19 для збільшення розрядності.

Основне використання асинхронних лічильників полягає в побудові всіляких дільників частоти, тобто пристроїв, що видають вихідний сигнал з частотою, у декілька разів меншою, ніж частота вхідного сигналу. В даному випадку нас цікавить не вихідний код лічильника, тобто не всі його розряди одночасно, а тільки один розряд, тому взаємні затримки окремих розрядів не грають ролі, повна затримка перемикання лічильника не має значення. Найпростіший приклад дільника частоти на два — це трігер в рахунковому режимі або лічильник, вихідним сигналом якого є вихід першого, молодшого розряду.

При побудові дільників частоти іноді важлива не тільки частота вихідного сигналу, але і його форма, його шпаруватість, тобто відношення періоду проходження імпульсів до тривалості цих імпульсів. В таких випадках частіше за все потрібен меандр, тобто цифровий сигнал з шпаруватістю, рівною двом (тривалість імпульсів рівна тривалості паузи між ними). Одержати меандр з будь-якого сигналу досить просто: треба використовувати додатковий дільник частоти на 2, правда при цьому частота вихідного сигналу зменшиться ще удвічі.

Найпростіший приклад такого дільника частоти на десять приведений на малюнку 25.6. В дільнику використаний лічильник ИЕ2, біля якого однорозрядний внутрішній лічильник включений після трьохрозрядного внутрішнього лічильника. Трьохрозрядний лічильник ділить частоту вхідного сигналу на 5, але вихідні імпульси мають шпаруватість, не рівну двом (вона рівна 5). Однорозрядний лічильник ділить частоту ще удвічі і одночасно формує меандр. Затримки перемикання розрядів лічильника один відносно одного на малюнку не показані (застосовуємо перший рівень представлення, логічну модель).

Малюнок 25.6. Дільник частоти на 10, що видає меандр.

Іноді виникає задача поділу частоти вхідного сигналу на довільне число раз (не в 10 і не в 2n, що легко забезпечується самою структурою стандартних лічильників). В цьому випадку можна організувати скидання лічильника при досягненні їм необхідного коду шляхом введення зворотних зв'язків.

Малюнок 25.7. Дільник частоти на 9 із зворотними зв'язками.

Наприклад, на малюнку 25.7 показаний найпростіший дільник частоти на 9 на основі лічильника ИЕ5. Досягнувши вихідним кодом значення 9 (тобто 1001) лічильник автоматично скидається на нуль по входах R1 і R2, і рахунок починається знову. В результаті частота вихідного сигналу в 9 разів менше частоти вхідного сигналу. При цьому шпаруватість вихідного сигналу не рівна двом. Тимчасова діаграма показана на малюнку для першого рівня уявлення (без урахування тимчасових затримок).

Якщо в числі, на яке треба ділити частоту більше дві одиниць (наприклад, 15, тобто 1111, або 13, тобто 1101), то для формування сигналу скидання треба використовувати елементи 2І, 3І або 4І для об'єднання всіх виходів, рівних одиниці. В результаті можна побудувати дільника вхідної частоти в будь-яке число раз від 2 до 2n, де N — число розрядів лічильника, що використовується. Правда, при організації зворотних зв'язків треба враховувати обмеження на швидкодію лічильника. Всі розряди, що використовуються для зворотного зв'язку, повинні встигнути перемкнутися за один період вхідного сигналу. Шпаруватість вихідного сигналу може приймати в даному випадку самі різні значення, наприклад, вихідний сигнал може представляти дуже короткі імпульси.

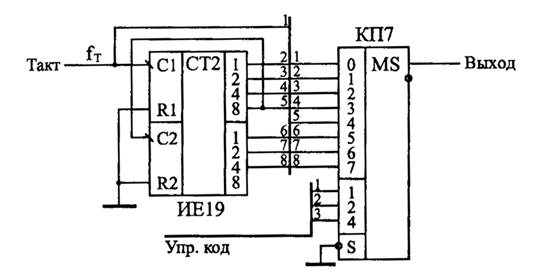

За допомогою асинхронних лічильників можна будувати також керовані дільники частоти, тобто такі дільники, вихідна частота яких визначається керуючим кодом. На малюнку 25..8 показаний дільник на 2n, де n — ціле. Восьмирозрядний лічильник ИЕ19 працює по вхідному сигналу з тактовою частотою fT, а вихідний мультиплексор з 8 входами КП7 передає на вихід схеми один з 7 розрядів лічильника або ж вхідний сигнал. Вибір номера каналу проводиться вхідним керуючим 3-розрядним кодом. Наприклад, при тактовій частоті fT = 10 Мгц, тобто при періоді вхідного сигналу 100 нс період вихідного сигналу може складати 100 нc, 200 нc, 400 нc, 800 нc, 1,6 мкс, 3,2 мкс, 6,4 мкс, 12,8 мкс.

Малюнок 25. 8. Керований дільник частоти на асинхронному лічильнику.

У момент перемикання управляючого коду на виході схеми можуть з'явитися небажані короткі імпульси, оскільки ніякої синхронізації управляючого коду не передбачено. Тому схема повинна працювати так: спочатку задається вхідний керуючий код, а вже потім дозволяється робота тієї схеми, на яку поступає сформований нашою схемою вихідний сигнал. В цьому випадку жодних проблем не буде. Не грають ролі в даному випадку і затримки перемикання розрядів лічильника, оскільки завжди використовується тільки його один розряд. Головне, щоб з частотою fT перемикався перший розряд лічильника.

Звичайно, використання асинхронних лічильників не обмежується тільки діленням частоти. У випадках, коли високої швидкодії не вимагається, коли перехідні процеси на виходах лічильника не мають значення (при правильній синхронізації), асинхронні лічильники цілком можуть замінити більш швидкі синхронні лічильники. Частка таких задач складає близько 20% від загального числа.

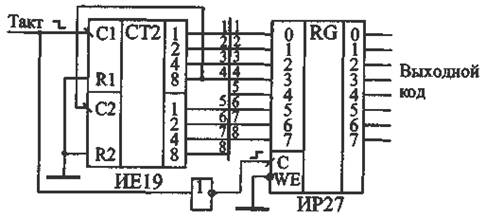

Якщо ж включити на виході асинхронного лічильника вихідний паралельний регістр (Малюнок 25.9), то можна забезпечити одночасне перемикання всіх вихідних розрядів лічильника.

Малюнок 25.9. Включення вихідного регістра для одночасного перемикання розрядів вихідного коду.

Дана схема працюватиме правильно, якщо період проходження вхідних тактових імпульсів буде більше, ніж час встановлення всіх розрядів лічильника (в нашому випадку — 8-розрядного лічильника ИЕ19). Інвертування необхідне, оскільки лічильник спрацьовує по негативному фронту вхідного сигналу, а регістр — по позитивному фронту. Хоча дане рішення усуває головний недолік асинхронного лічильника — неодночасність встановлення його вихідних розрядів, проте другий недолік — велика затримка встановлення вихідного коду — зберігається. Його усунути неможливо, можна тільки перейти на інші, більш швидкі лічильники.

На закінчення даного розділу треба відзначити, що асинхронні лічильники, як і інші цифрові схеми, пред'являють вимоги до тривалості вхідних сигналів. Наприклад, не повинні бути дуже короткими сигнали на тактових входах і на входах скидання і установки. Не повинні бути дуже затягнутими фронти вхідних сигналів. Тактові сигнали і сигнали скидання не повинні приходити з дуже малими затримками один відносно одного.

25.3. Синхронні лічильники з асинхронним перенесенням

Синхронні (або паралельні) лічильники характеризуються тим, що всі їх розряди в межах однієї мікросхеми перемикаються одночасно, паралельно. Це досягається істотним ускладненням внутрішньої структури мікросхеми в порівнянні з простими асинхронними лічильниками. В результаті повна затримка перемикання синхронного лічильника приблизно рівна затримці одного трігера, тобто синхронні лічильники набагато швидше за асинхронні, причому їх швидкодія не падає із зростанням кількості розрядів вихідного коду (звичайно, до певних меж).

Управління роботою синхронного лічильника набагато складніше, ніж у асинхронного лічильника, а кількість розрядів синхронних лічильників звичайно не перевищує чотирьох. Тому синхронні лічильники не завжди можуть успішно конкурувати з асинхронними лічильниками, особливо при невисоких вимогах до швидкодії. Зате і можливостей у синхронних лічильників, як правило, набагато більше, ніж в асинхронних, наприклад, вони забезпечують паралельний запис інформації в лічильник і інверсний режим рахунку.

Для об'єднання декількох синхронних лічильників з метою збільшення числа їх розрядів використовується спеціальний вихідний сигнал перенесення. Залежно від принципів формування сигналу перенесення і від принципів його використання синхронні (паралельні) лічильники діляться на лічильники з асинхронним (послідовним) перенесенням і лічильники з синхронним (паралельним) перенесенням (або повністю синхронні лічильники).

Синхронні лічильники з асинхронним перенесенням займають проміжне положення по швидкодії між асинхронними лічильниками і повністю синхронними лічильниками. Управління їх роботою простіше, ніж в синхронних лічильників, але складніше, ніж в асинхронних. Працюють дані лічильники по позитивному фронту вхідного сигналу (або, що те ж саме, по задньому фронту негативного сигналу). Основна суть їх роботи зводиться до наступного: всі розряди одного лічильника перемикаються одночасно, але при каскадуванні лічильників кожний наступний лічильник (даючий більш старші розряди) перемикається із затримкою щодо попереднього лічильника (даючого більш молодші розряди). Тобто затримка перемикання багаторозрядного лічильника збільшується в даному випадку не з кожним новим розрядом (як в асинхронних лічильників), а з кожною новою (наприклад, 4-розрядної) мікросхемою.

Сигнал перенесення в цих лічильників при прямому рахунку виробляється тоді, коли всі розряди рівні одиниці (досягнутий максимальний код) і коли приходить вхідний сигнал. Тому сигнал перенесення, що повторює вхідний сигнал, буде затриманий відносно вхідного сигналу. І саме цей сигнал перенесення використовується як вхідний для наступного лічильника при каскадуванні. Тобто вхідний сигнал другого лічильника затриманий відносно вхідного сигналу першого лічильника, вхідний сигнал третього лічильника затриманий відносно вхідного сигналу другого лічильника і т.д.

Тимчасова діаграма 4-розрядного синхронного лічильника з асинхронним перенесенням показана на малюнку 25.10. З малюнка видно, що розряди перемикаються одночасно по позитивному фронту вхідного сигналу (з деякою затримкою), а негативний сигнал перенесення також затриманий відносно вхідного негативного імпульсу. Зрозуміло, що перемикання розрядів лічильника, що працює з цим сигналом перенесення як вхідний, відбуватиметься з додатковою затримкою відносно перемикання розрядів даного лічильника.

Малюнок 25.10. Тимчасова діаграма роботи синхронного лічильника з асинхронним перенесенням.

Прикладами синхронних лічильників з асинхронним перенесенням можуть служити двійково-десятковий лічильник ИЕ6 і двійковий лічильник ИЕ7 (Малюнок 25.11). Вони повністю ідентичні по своїх можливостях і призначеннях входів і виходів, але тільки лічильник ИЕ6 рахує від 0 до 9, а лічильник ИЕ7 — від 0 до 15. Обидва лічильники реверсивні, забезпечують як прямий рахунок (по позитивному фронту на вході +1), так і зворотний рахунок (по позитивному фронту на вході -1). При прямому рахунку негативний сигнал перенесення утворюється на виході >15 (ИЕ7) або >9 (ИЕ6). Після досягнення вихідним кодом значення 0000, при зворотному (інверсному) рахунку негативний сигнал перенесення утворюється на виході <0. Є можливість скидання лічильника на нуль позитивним сигналом на вході R, а також можливість паралельного запису в лічильник коду з входів Dl, D2, D4, D8 по негативному сигналу на вході -WR. При паралельному записі інформації лічильники поводяться як регістри-замки, тобто вихідний код лічильника повторює вхідний код, поки на вході -WR присутній сигнал нульового рівня.

Малюнок 25.11. Синхронні лічильники з асинхронним перенесенням.

Вхід паралельного запису позначається іноді на схемах також -L, -С, а виходи перенесення позначаються також -CR і -BR.

Режими роботи лічильників ИЕ6 і ИЕ7 представлені в таблиці. 25.4.

Після скидання лічильник починає рахунок по позитивних фронтах на рахункових входах від нульового коду. Після паралельного запису рахунок починається від числа, записаного в лічильнику. Після переповнення лічильника ИЕ7 (досягнення коду 1111) при прямому рахунку виробляється негативний сигнал перенесення >15, повторюючий негативний вхідний імпульс на вході +1 із затримкою. Після досягнення коду 0000 при зворотному рахунку виробляється негативний сигнал перенесення <0, повторюючий негативний вхідний імпульс на вході з затримкою -1с. Так само працює і лічильник ИЕ6, але у нього переповнення виникатиме в режимі прямого рахунку досягнувши коду 1001.

Вхідні сигнали рахунку, запису і скидання не повинні бути дуже короткими. Не повинен бути дуже малим часовий зсув між сигналами на входах Dl — D8 і сигналом запису як на початку імпульсу запису, так і в його кінці (сигнал запису -WR повинен починатися після встановлення вхідного коду, а закінчуватися — до зняття вхідного коду).

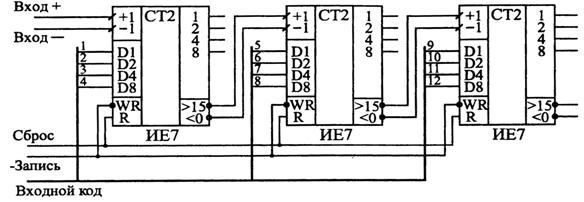

Об'єднання лічильників ИЕ7 і ИЕ6 для збільшення розрядності (каскадування) здійснюється дуже просто: потрібно виходи перенесення молодших лічильників (даючих молодші розряди вихідного коду) з'єднати з рахунковими входами старших лічильників (даючих старші розряди вихідного коду). На Малюнок 25. 1.12 показана організація 12-розрядного лічильника на трьох мікросхемах ИЕ7. Цей лічильник може рахувати як на збільшення (прямий рахунок), так і на зменшення (зворотний рахунок). Можливі також скидання і паралельний запис в лічильники вхідного коду. Розряди кожного наступного лічильника перемикатимуться одночасно, але із затримкою відносно перемикання розрядів попереднього лічильника. Так само об'єднуються і лічильники ИЕ6.

Якщо необхідно використовувати всі вихідні розряди багаторозрядного лічильника одночасно (як єдиний код), то необхідне виконання наступної умови:

T>(N-l) t3n+t3C

де Т — період вхідного сигналу, N — число з'єднаних мікросхем лічильників,

tЗn — час затримки перенесення одного лічильника, t3C — час затримки рахунку (перемикання вихідного коду) одного лічильника.

Малюнок 25. 12. Об'єднання лічильників ИЕ7 для збільшення розрядності.

Використання синхронних лічильників з асинхронним перенесенням дуже багатоманітне. Наприклад, вони можуть ділити частоту вхідного сигналу, рахувати вхідні імпульси, формувати пачки імпульсів, вимірювати тривалість тимчасового інтервалу, формувати сигнали заданої тривалості, вимірювати частоту вхідних імпульсів, послідовно перемикати вхідні і вихідні канали, формувати складні послідовності сигналів, перебирати адреси пам'яті і інше. Ми розглянемо лише декілька найтиповіших прикладів.

Як подільники частоти вхідного сигналу синхронні лічильники з асинхронним перенесенням дуже зручні, оскільки в них поєднується порівняно висока швидкість роботи з досить простим управлінням. Зручно також і те, що у них є режим зворотного рахунку. На цих лічильниках можна будувати подільники частоти з довільно змінним за допомогою вхідного коду коефіцієнтом поділу. Такі дільники знаходять, наприклад, широке використання в аналого-цифрових системах, що працюють з аналоговими сигналами різної частоти.

Найпростіший приклад 8-розрядного дільника частоти на лічильниках ИЕ7 показаний на малюнку 25.13.

На вхід лічильників подається 12-розрядний керуючий код, що визначає коефіцієнт розподілу вхідної частоти. Цей код записується в лічильники по сигналу перенесення <0 старшого лічильника. З цього коду починається потім рахунок на зменшення. Коли лічильники порахують кількість вхідних імпульсів, рівну вхідному коду, знову утвориться сигнал перенесення старшого лічильника і знову запише вхідний код в лічильники. Коефіцієнт розподілу буде рівний (N+1) при вхідному коді N. Негативний вихідний сигнал формою повторюватиме вхідний, але з повною затримкою перенесення, а його частота буде менше частоти вхідного сигналу в (N+1) раз. При 12-розрядному вхідному коді максимальний коефіцієнт розподілу складе 4096, а мінімальний — 1.

Малюнок 25.13. Дільник частоти з коефіцієнтом розподілу, вхідним кодом, що задається.

Щоб сформулювати умови правильної роботи даного дільника частоти, треба перш за все відзначити, що запис вхідного коду в лічильники проводиться негативним рівнем сигналу -WR, тобто переднім фронтом вхідного негативного імпульсу, а рахунок проводиться позитивним фронтом сигналу -1, тобто заднім фронтом вхідного негативного імпульсу. Звідси випливає, що вхідний імпульс повинен бути достатньо коротким. Якщо він записує код в лічильники своїм переднім фронтом, він вже не повинен своїм заднім фронтом перемикати лічильники по входу -1. Тому тривалість вхідного негативного імпульсу не повинна перевищувати повного часу перемикання лічильників і запису в них вхідного коду. В нашому випадку це три затримки перенесення і затримка запису в лічильник.

Якщо частота вхідного сигналу велика (наприклад, більше 10 Мгц), то нормальна тривалість вхідного сигналу виходить сама собою. Але частота вхідного сигналу не може бути й дуже великою. Інакше в процесі запису лічильник пропустить один з вхідних імпульсів або навіть декілька. Тобто від переднього фронту вхідного негативного сигналу до заднього фронту наступного вхідного негативного сигналу повинні встигнути спрацювати всі лічильники і повинен відбутися запис в лічильники (сумарний час затримки знову ж таки включить суму затримок перенесення всіх лічильників і затримку запису). Тобто обмеження на вхідну частоту буде тим жорсткіше, чим більше лічильників ми об'єднуємо для збільшення кількості розрядів. В даному випадку важлива саме кількість застосованих мікросхем, а не кількість розрядів, що використовуються, як в асинхронних лічильниках.

Для вирішення задачі підрахунку кількості вхідних імпульсів, що прийшли, необхідно всього лише об'єднати декілька мікросхем лічильників з метою отримання необхідного числа розрядів. Наприклад, якщо кількість вхідних імпульсів не перевищує 255, то достатньо два 4-розрядних лічильників, якщо воно не більше 65535, то треба об'єднати вже чотири 4-розрядні лічильники. Оскільки в цьому випадку нас цікавлять всі вихідні розряди одночасно, необхідно забезпечити, щоб за період вхідних імпульсів перемикалися всі мікросхеми лічильників.

Забезпечити одночасність перемикання всіх вихідних розрядів лічильника за рахунку вхідних імпульсів можна, як і у разі асинхронних лічильників, за рахунок включення вихідного паралельного регістра, що спрацьовує по фронту (Малюнок 25. 14). Дане рішення досить універсальне, воно може використовуватися в самих різних ситуаціях, коли необхідний весь вихідний код лічильника цілком. Код на виході регістра буде утримуватися протягом всього періоду вхідних імпульсів. Правда, швидкодія лічильника від цього не підвищується.

Малюнок 25.14. Включення вихідного регістра для одночасного перемикання розрядів вихідного коду.

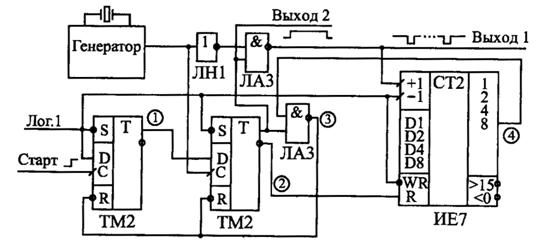

Малюнок 25.15. Формувач пачки з восьми імпульсів.

Формування пачки (групи) вхідних імпульсів із заданою кількістю імпульсів — досить поширена задача. Наприклад, таке формування необхідне при організації обміну інформацією в послідовному коді. Якщо в якості перетворювача паралельного коду в послідовний використовується 8-розрядний регістр зсуву, то йому в якості синхросигнала необхідна пачка з восьми імпульсів. Схема формувача такої пачки імпульсів показана на малюнку 25.15, а тимчасова діаграма її роботи — на малюнку 25.16.

Малюнок 25.16. Тимчасова діаграма роботи формувача пачки імпульсів.

По сигналу Старт (позитивний фронт) перемикається перший трігер, що використовується для синхронізації. По першому позитивному фронту тактового сигналу з генератора перемикається другий трігер, що дозволяє проходження імпульсів з генератора на вихід через елемент 2І-НІ, а також дозволяє роботу лічильника ИЕ7.

Після того, як на Вихід1 схеми пройдуть вісім негативних імпульсів, на виході 8 лічильника виробиться одиниця, що приведе до скидання в початкове нульове положення обох трігерів (коротким негативним імпульсом на виході нижнього на малюнку елементу 2І-НІ) і до заборони проходження імпульсів на вихід. Робота формувача поновиться після наступного сигналу Старт.

На основі лічильників досить просто будувати формувачі тимчасових інтервалів з тривалістю, що задається зовнішнім кодом. Такі формувачі знаходять широке використання, наприклад, в різних вимірювальних пристроях. Оскільки формувач тимчасових інтервалів звичайно працює з кварцовим тактовим генератором, можливі два підходи до його побудови.

При першому підході вхідний стартовий імпульс синхронізується з тактовим сигналом, внаслідок чого вихідний імпульс заданої тривалості може початися не відразу після стартового імпульсу, а через якийсь час, менше періоду тактового сигналу. Тривалість формованого тимчасового інтервалу буде в цьому випадку абсолютно точно відома і буде рівна цілому числу періодів тактового генератора. Саме так було зроблено в попередній розглянутій нами схемі (сигнал Вихід 2 на малюнку 25.15 якраз і буде формованим сигналом із заданою тривалістю).

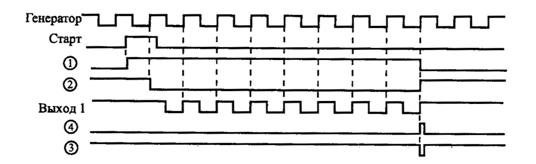

При другому підході вихідний імпульс заданої тривалості починається відразу після вхідного сигналу, але тривалість його може відрізнятися від заданої на якийсь час, менший періоду тактового сигналу. Іноді це більш прийнятне рішення, особливо при великих тривалостях вихідного сигналу, значне більших, ніж період тактового сигналу. Схема формувача тимчасового інтервалу, побудованого відповідно до цього другого підходу, показана на малюнку 25.17.

Малюнок 25.17. Формувач тимчасового інтервалу

Робота схеми починається з подачі короткого негативного імпульсу -Старт. Він перекидає трігер, який дозволяє роботу лічильників зняттям сигналу паралельного запису -WR. По негативному фронту вхідного сигналу починається позитивний вихідний сигнал заданої тривалості. Лічильники починають рахувати на зменшення коду по позитивних фронтах тактового сигналу з генератора. Коли вони долічать до нуля, виробляється сигнал перенесення, що перекидає трігер в початкове положення. Робота схеми поновиться після наступного сигналу -Старт.

Якщо вхідний код рівний 1, то тривалість вихідного сигналу складе від Т до 2Т, де Т — період тактового сигналу. Якщо вхідний код рівний N (до 255), то тривалість вихідного сигналу складе від NT до (N+1) T залежно від моменту приходу вхідного сигналу по відношенню до тактового сигналу. Абсолютна похибка витримки тривалості вихідного сигналу у будь-якому випадку не перевищує періоду тактового сигналу Т.

Цю ж саму схему цілком можна використовувати в тих випадках, коли необхідно одержати код, який прямує від заданого числа до нуля. При цьому сигнал з виходу трігера буде тільки внутрішнім сигналом схеми, а вихідними сигналами схеми будуть вихідні розряди лічильників.

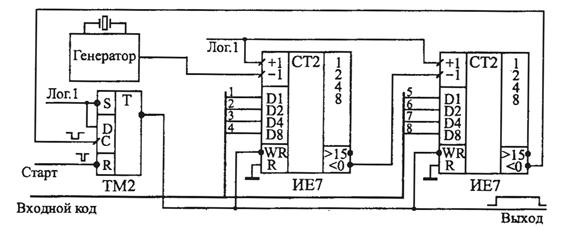

Іноді буває необхідне сформувати імпульс необхідної тривалості, але одночасно мати не спадаючий, а зростаючий код (від нуля до заданого значення). У такому разі схема вийде дещо складніше. Приклад можливого рішення формувача імпульсу заданої тривалості показаний на малюнку 25.18.

По сигналу Старт (позитивний фронт) перекидається лівий по малюнку трігер, який починає формувати вихідний сигнал і дозволяє роботу лічильника (знімаючи сигнал скидання R). Лічильник рахує на збільшення по позитивних фронтах тактового сигналу від нуля. Коли вихідний код лічильника досягає величини вхідного коду, спрацьовує правий по малюнку трігер, завершальний процес формування вихідного сигналу. Лічильник скидається в нуль, правий трігер по наступному фронту потрапляє в початкове положення. Новий цикл почнеться з приходом наступного сигналу Старт.

Малюнок 25.18. Формувач імпульсу заданої тривалості (варіант з наростаючим кодом).

Якщо вхідний код рівний 1, то тривалість вихідного сигналу складе від Т до 2Т, де Т — період тактового сигналу генератора. Якщо вхідний код рівний N, то тривалість вихідного сигналу буде рівна від NT до (N+1)T залежно від тимчасового зсуву між сигналом Старт і тактовим сигналом. У будь-якому випадку абсолютна похибка часу затримки вихідного сигналу не перевищить періоду тактового сигналу Т.

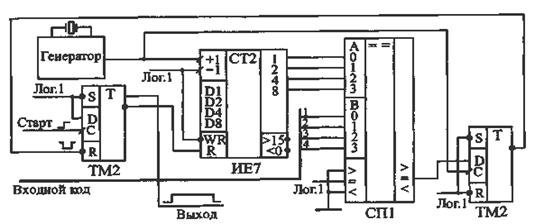

Лічильники також широко застосовуються в різних вимірниках тривалості вхідних сигналів. Для цього вони відлічують імпульси тактового кварцового генератора протягом тривалості вхідного сигналу. Після закінчення вхідного сигналу в лічильнику залишається код, пропорційний тривалості цього сигналу. Приклад практичної схеми такого вимірника показаний на малюнку 25.19.

Малюнок 25.19. Вимірювач тривалості вхідного сигналу

Малюнок 25.20. Тимчасова діаграма роботи вимірювача тривалості вхідного сигналу.

Робота схеми починається по короткому керуючому імпульсу Старт, який скидає лічильник на нуль і переводить всю схему в режим рахунку, дозволяючи проходження сигналу з тактового генератора на вхід +1 лічильника при позитивному вхідному сигналі. З початком вхідного сигналу імпульси з генератора поступають на вхід лічильника, і лічильник їх рахує. Після закінчення вхідного сигналу надходження імпульсів на вхід лічильника припиняється, трігер перекидається в початкове положення і повідомляє негативним фронтом на своєму інверсному виході про готовність вихідного коду (сигнал Готовність). Робота схеми поновиться по наступному імпульсу Старт. Тимчасова діаграма роботи вимірника тривалості вхідного сигналу приведена на малюнку 25.20.

Вихідний код N вимірювача пов'язаний з тривалістю вхідного сигналу t простим співвідношенням:

t = NT

де Т — період тактового сигналу. Абсолютна похибка вимірювання не перевищує величини ±Т. Тому для зменшення відносної похибки вимірювання необхідно збільшувати частоту тактового генератора і збільшувати розрядність лічильника.

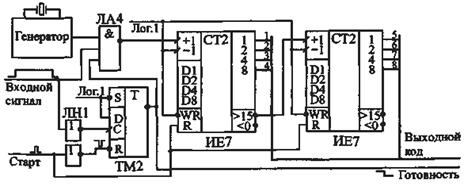

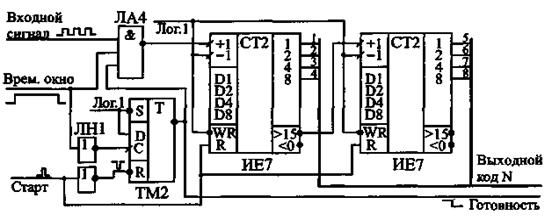

Лічильники також застосовуються і для вимірювання частоти вхідного цифрового сигналу.

Частоту вхідного сигналу можна виміряти двома шляхами: непрямим, тобто вимірюванням періоду вхідного сигналу (за принципом, розглянутим тільки що) і обчисленням частоти (по формулі: fвх = 1/Твх) або ж прямим вимірюванням частоти. Перший метод вимагає обчислень за допомогою комп'ютера або мікроконтролера, другий не вимагає ніяких додаткових обчислень. Тому ми розглянемо реалізацію методу прямого вимірювання частоти.

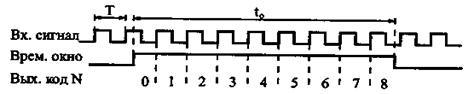

Відповідно до цього методу необхідно сформувати тимчасове вікно із заданою тривалістю to, протягом якого треба порахувати кількість N періодів вхідного сигналу Т (Малюнок 25.21). В цьому випадку виконуватиметься співвідношення:

t0 = NT або f=N/t0

де f — це частота вхідного сигналу, рівна 1/Т. Тобто частота вхідного сигналу пропорційна коду N, а коефіцієнт пропорційності рівний l/t0. Якщо, наприклад, вибрати t0 = 1с, то код N буде рівний частоті вхідного сигналу в герцах, а при t0 = 1 мс код N буде рівний частоті вхідного сигналу в кілогерцах.

Малюнок 25.21. Вимірювання частоти вхідного сигналу прямим методом.

Якщо тривалість тимчасового вікна —постійна величина, то похибка вимірювання частоти визначатиметься тільки похибкою підрахунку коду N. Абсолютна похибка підрахунку коду N не перевищить одиниці, а відносна похибка не буде більша ніж 1/N. Зрозуміло, що для збільшення точності вимірювання частоти треба збільшувати N, тобто необхідно збільшувати тривалість тимчасового вікна t0. Проте при цьому автоматично збільшується час вимірювання.

Схема вимірювача частоти (Малюнок 25. 1.22) практично не відрізняється від схеми вимірювача тривалості вхідного сигналу (Малюнок 25.19). Тільки в даному випадку як вимірюваний сигнал буде використовуватись сигнал тимчасового вікна, а як тактовий сигнал — вхідний сигнал. Для формування сигналу тимчасового вікна можна застосувати схему малюнок 25.15 (сигнал Вихід 2), яка забезпечує постійну тривалість вихідного сигналу.

Малюнок 25. 22. Вимірювач частоти вхідного сигналу прямим методом.

Ще одне широке поширене використання лічильників — послідовне перемикання (сканування) декількох пристроїв, вузлів, індикаторів, каналів передачі і т.д. Існує, наприклад, група пристроїв, які повинні з тих або інших причин працювати не одночасно, а по черзі, так, що в кожний момент активним є тільки один пристрій, причому черга ця замкнута в кільце, і після останнього пристрою починає працювати перше. Або ж є декілька каналів зв'язку (вхідних або вихідних ліній), які треба так само по черзі підключати до одного виходу (при вихідних каналах) або до одного входу (при вхідних каналах).

У всіх подібних випадках опитування, перемикання, сканування може проводити лічильник з потрібним числом розрядів. Лічильник з числом розрядів n може обслуговувати 2n пристроїв (або каналів).

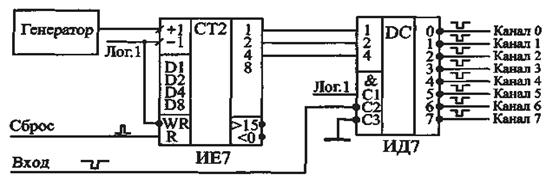

Малюнок 25.23. Схема послідовного перемикання вихідних каналів.

В якості першого прикладу розглянемо схему перемикання вихідних каналів (Малюнок 25.23). Вона послідовно, по черзі, циклічно комутує один вхідний сигнал на вісім виходів, для чого використовуються лічильник, який тактується сигналом задаючого генератора, і дешифратор, що працює в якості демультиплексора. Кожний з вихідних каналів активний (тобто підключений) протягом одного періоду тактового сигналу, а потім пасивний (тобто відключений) протягом семи періодів тактового сигналу. Передбачена можливість початкового скидання схеми за допомогою сигналу Скидання.

Використовуючи дану схему, треба враховувати, що в момент перемикання каналів може спотворюватися (обрізатися) вихідний сигнал. Тому краще всього забезпечити, щоб вхідний сигнал приходив тільки тоді, коли перемикання каналів не проводиться. Або на час передачі взагалі зупиняти процес перебору каналів шляхом заборони проходження імпульсів з генератора на вхід лічильника, а після закінчення передачі знову дозволяти послідовний перебір каналів.

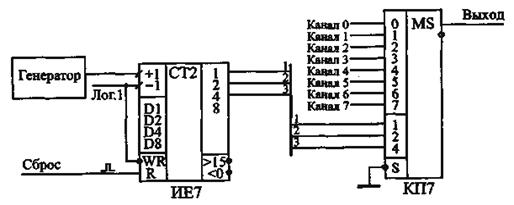

Малюнок 25.24. Схема послідовного перемикання вхідних каналів.

Другий приклад, який ми розглянемо, це схема, яка вирішує протилежну задачу — перемикання вхідних каналів (Малюнок 25.24). Дана схема послідовно, циклічно передає один з восьми вхідних сигналів на вихід. Як і у попередньому випадку, перебір каналів здійснюється лічильником, тактованим сигналом з генератора. Безпосередньо комутація сигналів проводиться мультиплексором, на адресні входи якого подаються три розряди лічильника. Передбачена можливість початкового скидання схеми за допомогою сигналу Скидання.

У момент перемикання каналів тут також можливе спотворення (обрізання) комутованих сигналів. Тому бажано забезпечити передачу сигналів в мить, коли перемикання каналів немає. Або ж треба зупиняти процес перебору каналів на час прийому сигналу з вибраного каналу шляхом заборони проходження тактових імпульсів на вхід лічильника, а потім знову запускати перебір каналів.

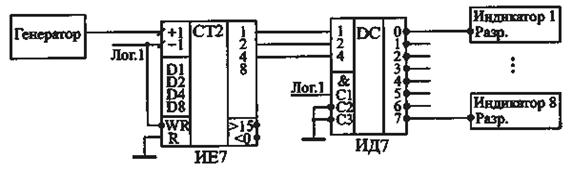

Ще одне використання лічильників з цієї ж області полягає в організації так званої динамічної індикації.

Суть динамічної індикації полягає в наступному. Якщо використовується табло з декількох індикаторів (одиночних світлодіодів, світлодіодних семисегментних індикаторів, світлодіодних матричних індикаторів і т. д.), то зовсім не обов'язково, щоб всі ці індикатори горіли постійно, одночасно. Можна запалювати їх по черзі, що істотно скоротить споживаний всією схемою напругу живлення. Наприклад, якщо в кожний момент часу горить тільки один індикатор ,з восьми існуючих, то струм споживання індикаторів скоротиться у вісім разів. Враховуючи, що кожний світлодіод, що світиться, вимагає струм 1—5 мА, такий підхід може дати великий виграш, особливо у разі матричних індикаторів, що містять декілька десятків світлодіодів. А інерційність людського ока призводить до того, що спалахи світла з частотою більше 20 Гц сприймаються як безперервне свічення. Отже при достатній частоті перебору індикаторів оку не буде помітне їх послідовне включення.

На малюнку 25.25 приведений приклад схеми динамічної індикації на восьми індикаторах. Для послідовного перебору індикаторів застосовується лічильник, сполучений з дешифратором. Вихідні сигнали дешифратора використовуються як сигнали, що дозволяють свічення індикаторів. Частота сигналу тактового генератора, з яким працює лічильник, повинна складати не менше 160 Гц, щоб кожний індикатор спалахував не рідше, ніж з частотою 20 Гц. При цьому не можна також вибирати дуже велику частоту тактового генератора, оскільки в моменти перемикання струм споживання мікросхем сильно зростає через паразитні ємності і при великій частоті весь ефект зниження споживання може піти нанівець.

Малюнок 25.25. Схема динамічної індикації на восьми індикаторах.

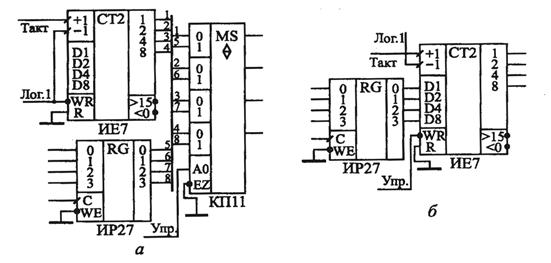

Лічильники часто використовують також для організації всіляких таймерів, годинника, тобто схем рахунку часу, вихідний код яких необхідно час від часу читати. Для цього на вхід лічильника подається сигнал зразкової частоти з кварцового генератора. При цьому виникає наступна проблема. Якщо читання відбувається в той момент, коли лічильники перемикаються, то з виходів лічильників може бути порахований випадковий код, який не відповідає ні попередньому сталому значенню, ні подальшому сталому значенню. Можна, звичайно, на час читання коду зупинити рахунок, але тоді хід годинника зіб'ється.

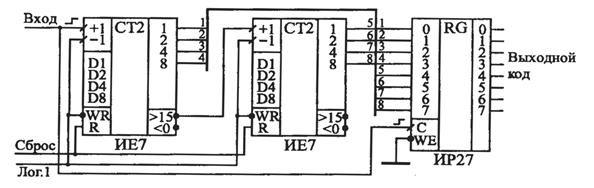

Малюнок 25.26. Схема таймера з читанням вихідного коду.

Приклад рішення даної проблеми приведений на малюнку 25.26. Тут вихідний код лічильника на кожному такті записується у вихідний регістр з дозволом запису ИР27. А у момент читання коду (при позитивному сигналі Читання) запис в регістр забороняється. В результаті протягом всієї тривалості сигналу Читання вихідний код схеми буде незмінним, хоча лічильник продовжуватиме рахувати без жодних перешкод, і хід годинника не зіб'ється.

Цікава особливість лічильників ИЕ6 і ИЕ7 полягає в тому, що вони можуть працювати не тільки в режимі рахунку, але і в режимі плвторювача вхідних сигналів даних. В режимі паралельного запису в лічильник при нульовому сигналі на вході -WR вихідні сигнали лічильника повторюватимуть будь-які зміни вхідних сигналів даних, тобто лічильник працює по суті як регістр, що спрацьовує по рівню стробуючого сигналу. У ряді випадків така особливість дуже зручна, оскільки вона дозволяє істотно спростити апаратуру.

Малюнок 25.27. Варіанти мультиплексування вихідного коду лічильника із застосуванням мультиплексора (а) і без нього (б).

Нехай, наприклад, необхідно видавати на вхід схеми один з двох вхідних кодів: код з лічильника, або код з регістра (тобто потрібне мультиплексування двох кодів). Цю задачу можна вирішити, застосовуючи двохканальний мультиплексор (Малюнок 25.27,a), а можна вирішити простіше — подаючи код з регістра на входи даних лічильника і переводячи в потрібний момент лічильник в режим паралельного запису (Малюнок 25.27,б). В обох випадках перемикання кодів, що подаються на вихід схеми, проводиться сигналом Упр. Правда, в другому випадку лічильник відновлює свій рахунок (після зняття сигналу запису -WR) з коду, записаного в регістр. Якщо це неприйнятно, то можна скористатися входом скидання лічильника на нуль R.

25.4 Синхронні лічильники

Синхронні (або паралельні) лічильники є самим швидкодійним різновидом лічильників. Нарощування їх розрядності при дотриманні певних умов не приводить до збільшення повної затримки спрацьовування. Тобто можна вважати, що саме синхронні лічильники працюють як ідеальні лічильники, всі розряди яких спрацьовують одночасно, паралельно. Затримка спрацьовування лічильника в цьому випадку приблизно рівна затримці спрацьовування одного трігера. Досягається така швидкодія істотним ускладненням внутрішньої структури мікросхеми.

Разом з тим недоліком синхронних лічильників є складніше управління їх роботою в порівнянні з асинхронними лічильниками і з синхронними лічильниками з асинхронним перенесенням. Тому синхронні лічильники доцільно застосовувати тільки в тих випадках, коли дійсно потрібна дуже висока швидкодія, дуже висока швидкість перемикання розрядів. Інакше ускладнення схеми управління може не бути виправдано.

Малюнок 25.28. Тимчасова діаграма роботи синхронних двійкових лічильників.

Тимчасова діаграма роботи синхронного лічильника (Малюнок 25.28) відрізняється від тимчасової діаграми синхронного лічильника з асинхронним перенесенням способом формування сигналу перенесення, що використовується при тому, що каскадує лічильники для збільшення розрядності. Сигнал перенесення CR виробляється в даному випадку тоді, коли всі виходи лічильника встановлюються в одиницю (при прямому рахунку) або в нуль (при зворотному, інверсному рахунку). Вхідний тактовий сигнал в утворенні сигналу перенесення при цьому участь не бере.

Тому при, каскадуванні (сумісному включенні для збільшення розрядності), наприклад, двох лічильників тактові входи С обох лічильників об'єднуються, а сигнал перенесення першого лічильника подається на вхід дозволу рахунку (ЕСТ) другого лічильника. В результаті другий лічильник рахуватиме кожний шістнадцятий вхідний тактовий імпульс (оскільки він спрацьовуватиме тільки при перенесенні від першого лічильника). Вихідні сигнали другого лічильника перемикатимуться по фронту загального тактового сигналу одночасно з вихідними сигналами першого лічильника. Умовою правильної роботи буде в даному випадку наступне: за періодом тактового сигналу повинен встигнути виробитися сигнал перенесення першого лічильника.

Малюнок 25.29. Синхронні лічильники стандартних серій.

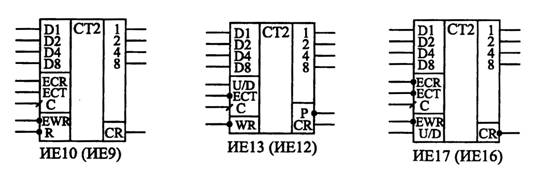

У стандартні серії мікросхем входять декілька різновидів синхронних (паралельних) лічильників (Малюнок 25.29). Розрізняються вони способом рахунку (двійкові або двійково-десяткові, реверсивні або не реверсивні), керуючими сигналами (наявністю або відсутністю сигналу скидання). Всі лічильники рахують по позитивному фронту тактового сигналу, всі мають вихід перенесення CR і входи розширення для того, щоб здійснити каскадування. Всі лічильники мають можливість паралельного запису інформації.

Лічильники ИЕ9 і ИЕ10 відрізняються один від одного тільки тим, що ИЕ9 — двійково-десятковий, а ИЕ10 — двійковий. Мікросхеми мають вхід асинхронного скидання -R, по нульовому рівню на якому всі виходи лічильника скидаються на нуль. Рахунок (тільки прямою) проводиться по позитивному фронту на тактовому вході С. Паралельний запис здійснюється синхронно, по позитивному фронту на тактовому вході С при встановленому на нуль сигналі дозволу запису -EWR. Сигнали ЕСR (Enable Carry — дозвіл перенесення) і ЕСТ (Enable Count — дозвіл рахунку) використовуються при каскадуванні мікросхем. Різниця між цими сигналами в тому, що сигнал ЕСR не тільки забороняє рахунок, як сигнал ЕСТ, але ще і забороняє вироблення сигналу перенесення CR. Рахунок йде при одиничних сигналах на обох входах ЕСТ і ЕСТ і при одиничному сигналі на вході -EWR. Позитивний сигнал перенесення CR виробляється при максимально можливому коді на виходах лічильника (15 для ИЕ10 і 9 для ИЕ9) і при позитивному сигналі на вході ЕСR. Режими роботи лічильників ИЕ9 і ИЕ10 представлені в таблиці 25.5.

Лічильники ИЕ12 (двійково-десятковий) і ИЕ13 (двійковий) відрізняються від ИЕ9 і ИЕ10 тим, що вони реверсивні, тобто допускають як прямий, так і зворотний рахунок. Крім того, у них дещо інше управління. Рахують вони також по позитивному фронту тактового сигналу С при нульовому рівні на вході дозволу рахунку ЕСТ. Прямий рахунок здійснюється при нульовому рівні на вході управління U/D, зворотний — при одиничному рівні на вході U/D. Перемикання рівнів на входах U/D і ЕСТ допускається тільки при позитивному сигналі на тактовому вході С. Скидання лічильників ИЕ12 і ИЕ13 на нуль не передбачене, але є можливість асинхронного паралельного запису інформації по нульовому рівню сигналу паралельного запису -WR.

Позитивний сигнал на виході паралельного перенесення CR з'являється досягши максимального коду (15 для ИЕ13 і 9 для ИЕ12) при прямому рахунку або досягши нульового коду при зворотному (інверсному) рахунку. Є також вихід послідовного перенесення Р, негативний імпульс на якому виробляється при позитивному сигналі CR і повторює негативний імпульс на тактовому вході С (аналогічно розглянутим раніше лічильникам ИЕ6 і ИЕ7).

Режими роботи лічильників ИЕ12 і ИЕ13 представлені в таблиці 25.6.

Мікросхеми ИЕ16 (двійково-десятковий лічильник) і ИЕ17 (двійковий лічильник) відрізняються від розглянутих синхронним паралельним записом по фронту тактового сигналу С, можливістю прямого і зворотного рахунку і відсутністю сигналу скидання на нуль.

Спрацьовують лічильники ИЕ16 і ИЕ17 по позитивному фронту тактового сигналу С. При нульовому рівні на вході дозволу запису -EWR по фронту сигналу С в лічильник записується інформація з входів даних Dl, D2, D4, D8. При одиничному рівні на вході -EWR по позитивному фронту сигналу С відбувається рахунок. Напрям рахунку визначається входом U/D: при одиниці на цьому вході рахунок прямий, при нулі — зворотний. Є два входи розширення: вхід дозволу рахунку -ЕСТ і вхід дозволу перенесення -ECR. Відрізняються ці два входи тим, що сигнал -ECR не тільки забороняє рахунок, як сигнал -ЕСТ, але ще і забороняє вироблення сигналу перенесення. Перемикання рівнів на входах U/D, -ЕСТ і -ECR треба проводити тільки при одиничному рівні на тактовому вході С.

Негативний сигнал перенесення -CR (синхронний) виробляється при досягненні на виходах лічильника максимального коду (15 для ИЕ7 або 9 для ИЕ16) при прямому рахунку або нульового коду при зворотному рахунку.

Режими роботи лічильників ИЕ16 і ИЕ17 приведені в таблиці 25.7.

Можливості використання синхронних (паралельних) лічильників дуже широкі. Достатньо сказати, що вони без жодних проблем можуть замінити у всіх схемах як асинхронні (послідовні) лічильники, так і синхронні лічильники з асинхронним (послідовним) перенесенням. При необхідності досягнення максимальної швидкодії вони мають великі переваги в порівнянні зі всіма іншими лічильниками. Їх вихідний код встановлюється одночасно при будь-якій кількості розрядів без використання додаткових вихідних регістрів (які були потрібні у разі асинхронних лічильників і синхронних лічильників з асинхронним перенесенням).

Ми розглянемо всього декілька схем, що ілюструють характерні особливості саме синхронних лічильників.

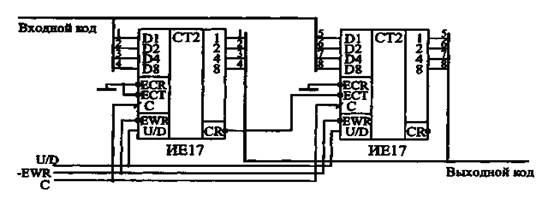

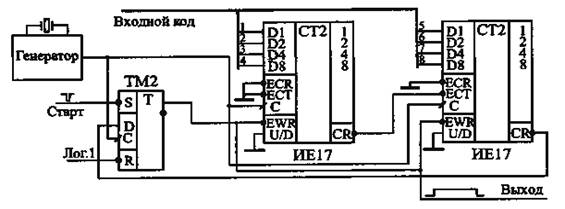

Спочатку зупинимося на методах каскадування лічильників. На відміну від інших типів лічильників синхронні лічильники можна з’єднувати різними способами, причому спосіб з'єднання різний для різної кількості мікросхем. Як приклад візьмемо мікросхеми ИЕ17.

При об'єднанні двох лічильників (Малюнок 25.30) жодних проблем не виникає: вихід перенесення -CR молодшого лічильника з'єднується з входом дозволу рахунку старшого лічильника -ЕСТ. На входи -ECR обох лічильників подається нульовий рівень. Умова правильної роботи буде простою і легко здійснимою: період тактового сигналу С не повинен бути менше ніж затримка вироблення сигналу перенесення CR.

Малюнок 25. 30. Об'єднання двох лічильників ИЕ17.

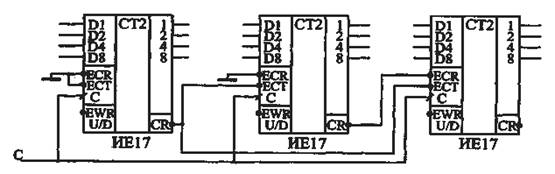

При об'єднанні трьох лічильників ситуація дещо ускладнюється (Малюнок 25.31). Сигнал з вихіду перенесення першого лічильника подається на входи -ЕСТ другого і третього лічильників. Сигнал з вихіду перенесення другого лічильника подається на вхід -ECR третього лічильника. В результаті третій лічильник рахуватиме тільки тоді, коли є перенесення як в першого лічильника, так і в другого лічильника. На малюнку для простоти не показано підключення вхідних і вихідних сигналів, що не беруть участь в каскадуванні.

Малюнок 25. 31. Об'єднання трьох лічильників ИЕ17.

Умова правильної роботи схеми залишається тією, що і у разі двох лічильників: період тактового сигналу С не повинен бути меншим затримки вироблення сигналу перенесення CR.

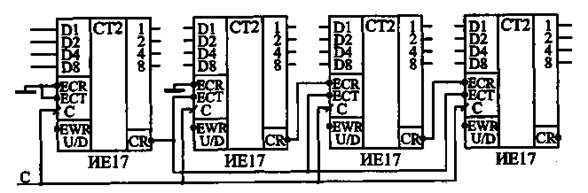

При об'єднанні чотирьох (і більше) лічильників вже виникає проблема, оскільки в старших лічильників не залишається вільних керуючих входів для збирання всіх сигналів перенесення більш молодших лічильників. Тому в даному випадку використовується здатність вхідного сигнал -ECR забороняти вихідний сигнал перенесення -CR (Малюнок 25.32). На четвертий і подальші лічильники подаються вже не сигнали перенесення зі всіх попередніх лічильників, а тільки з першого і з попереднього. На малюнку для простоти не показано підключення входів і виходів, що не беруть участь безпосередньо в каскадуванні.

Малюнок 25. 32. Об'єднання чотирьох лічильників ИЕ17.

При такому включенні відбувається вже накопичення затримок сигналів перенесення. Умова правильної роботи всіх лічильників буде наступна: період тактового сигналу С не повинен бути меншим ніж максимальна сумарна затримка сигналів перенесення до входу іншого лічильника. При об'єднанні чотирьох лічильників в цю максимальну затримку входять затримка сигналу перенесення -CR мікросхеми відносно фронту сигналу С і затримка сигналу перенесення -CR відносно сигналу -ECR. При об'єднанні п'яти лічильників додасться ще одна затримка сигналу перенесення -CR віднлсно сигналу -ECR і т.д. Тому із збільшенням кількості об'єднуваних лічильників знижуватиметься допустима тактова частота.

При необхідності об'єднання великої кількості лічильників (більше чотирьох) можна уникнути накопичення сумарної затримки перенесення, включивши на входах старших лічильників -ЕСТ логічні елементи АБО з потрібним числом входів. Ці елементи повинні збирати всі сигнали перенесення з більш молодших лічильників, тобто на їх виходах повинен бути нуль тоді, коли сигнали -CR всіх попередніх лічильників нульові. При цьому, правда, в сумарну затримку перенесення, яка не повинна перевищувати періоду тактового сигналу С, ввійдуть затримки цих самих елементів АБО.

У будь-якому випадку при виконанні умови правильної роботи лічильників схема працюватиме як ідеальний лічильник, тобто всі розряди багатокаскадного лічильника перемикатимуться одночасно.

А зараз розглянемо деякі схеми на основі синхронних лічильників.

Керований дільник частоти з коефіцієнтом перерахунку, вхідним кодом, що задається, реалізується на синхронних лічильниках досить просто (Малюнок 25.33). Сигнал перенесення -CR старшого лічильника подається на вхід дозволу запису -EWR. Лічильники працюють в режимі зворотного рахунку (на вхід U/D поданий сигнал логічного нуля).

Малюнок 25. 33. Керований дільник частоти.

При досягненні всіма лічильниками нульового коду виробляється сигнал перенесення -CR, що переводить лічильники в режим паралельного запису вхідного керуючого коду. Наступним позитивним фронтом тактового сигналу С вхідний код записується в лічильники. Це приводить до нового циклу рахунку від вхідного коду до нуля.

Коефіцієнт перерахунку дільника частоти рівний (N+1), де N — вхідний код, який може приймати значення від 1 до (2n- 1), де n — кількість розрядів коду. Умова правильної роботи дільника частоти наступна: період тактового сигналу не повинен бути меншим повної затримки перенесення. Тривалість вихідного сигналу дільника частоти рівна періоду тактової частоти.

Наступна схема — формувач тимчасового інтервалу заданої тривалості (Малюнок 25.34) демонструє, як треба використовувати вихідний сигнал перенесення синхронних лічильників при необхідності організації разового (не періодичного) циклу роботи.

Робота формувача починається по короткому негативному імпульсу -Старт, що перекидає управляючий трігер на одиницю і початковий вихідний сигнал. Позитивний сигнал з виходу трігера переводить 8-розрядний синхронний лічильник з режиму паралельного запису вхідного коду в режим рахунку (по входу -EWR). Рахунок на зменшення йде по позитивних фронтах тактового сигналу з генератора. Коли лічильник долічить до нуля, наступним позитивним фронтом тактового сигналу нульовий сигнал перенесення -CR буде записаний в трігер. Тим самим буде завершений вихідний сигнал, а лічильник буде переведений в режим паралельного запису. Наступний цикл роботи формувача почнеться по сигналу -Старт.

Малюнок 25.34. Формувач інтервалу заданої тривалості.