|

Тема 24. Регістри

24.1. Загальні поняття.

Регістрами (англійське Register) є, по суті, кілька D-тригерів (звичайно від 4 до 16), сполучених між собою тим або іншим способом. Тому принципової різниці між ними і окремими D-тригерами не існує. Правда, трігери, що входять до складу регістрів, не мають такої кількості різноманітних управляючих входів, як одиночні трігери.

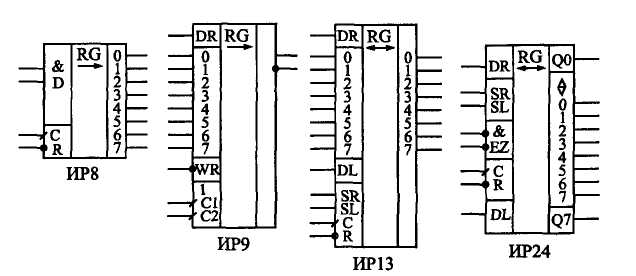

На схемах регістри позначаються буквами RG. У вітчизняних серіях мікросхем регістрам відповідають букви ИР. Всі регістри діляться на дві великі групи (малюнок 24.1):

• паралельні регістри;

• регістри зсуву (або зсувні регістри).

Малюнок 24.1. Структура паралельного регістра (а) і зсувного регістра (б).

Існують і регістри інших типів, але вони застосовуються набагато рідше, ніж паралельні і зсувні, оскільки мають вузькоспеціальне призначення.

В паралельних регістрах (а) кожний з трігерів має свій незалежний інформаційний вхід (D) і свій незалежний інформаційний вихід. Тактові входи (З) всіх трігерів сполучені між собою. В результаті паралельний регістр є багаторозрядним, багатовходовим трігером.

В зсувних регістрах (в) всі трігери сполучені в послідовний ланцюжок (вихід кожного попереднього трігера сполучений з входом D наступного трігера). Тактові входи всіх трігерів (З) з'єднані між собою. В результаті такий трігер може розглядатися як лінія затримки, вхідний сигнал якої послідовно перезаписується з трігера в трігер по фронту тактового сигналу С. Інформаційні входи і виходи трігерів можуть бути виведені назовні, а можуть і не виводитися залежно від функції, виконуваної регістром.

Паралельні регістри у свою чергу діляться на дві групи:

• регістри, що спрацьовують по фронту управляючого сигналу С (або тактовані регістри);

• регістри, що спрацьовують по рівню управляючого сигналу С (або стробовані регістри).

Частіше всього в цифрових схемах використовуються регістри, керовані фронтом (тобто тактовані), проте і стробовані регістри мають своє коло задач, в яких їх ніщо не може замінити.

24.2. Регістри, що спрацьовують по фронту

Принцип дії регістрів, що спрацьовують по фронту тактового сигналу, нічим не відрізняється від принципу дії D-тригера. По позитивному фронту тактового сигналу С кожний з виходів регістра встановлюється в той рівень, який був у цей момент на відповідному даному виходу вході D, і зберігається таким до приходу наступного позитивного фронту сигналу С. Тобто якщо трігер запам'ятовує один сигнал (один двійковий розряд, один біт), то регістр запам'ятовує відразу декілька (4, 6, 8, 16) сигналів (декілька розрядів, бітів). Пам'ять регістра зберігається до моменту виключення живлення схеми.

В стандартні серії входить декілька типів паралельних регістрів, що спрацьовують по фронту (малюнок 24.2). Розрізняються вони кількістю розрядів, наявністю або відсутністю інверсних виходів, наявністю або відсутністю входу скидання (-R) або дозволу запису (-WE), а також типом вихідних каскадів (2С або ЗС) і відповідно наявністю або відсутністю входу дозволу -EZ. Іноді на схемах тактовий вхід С позначається WR - сигнал запису в регістр.

Малюнок 24.2. Паралельні регістри стандартних серій, що спрацьовують по фронту.

Більшість регістрів має вісім розрядів, тобто запам'ятовують один байт інформації. Регістр ТМ8 в довідниках звичайно називається чотири D-тригера (він і в імені має букви ТМ), хоча він цілком може розглядатися і як регістр, оскільки тактовий вхід С і вхід скидання -R у всіх чотирьох трігерів з'єднані між собою.

Таблиці істинності регістрів дуже прості і не відрізняються принципово від таблиці істинності D-тригерів. Відмінність від трігерів з'являється тільки у разі наявності у регістра додаткових управляючих входів дозволу запису -WE і дозволу виходу -EZ. Як приклади нижче приведені таблиці істинності регістра ИР27 і регістра ИР37 (таблиці 24.1. і 24.2 відповідно). По переходу тактового сигналу С з 0 в 1 (позитивний фронт) обидва регістри записують в себе вхідну інформацію.

Всі регістри, що мають вихід з трьома станами, забезпечують підвищену здатність навантаження. Затримка перемикання регістрів приблизно відповідає затримці перемикання трігерів. Всі тимчасові обмеження, що накладаються на вхідні сигнали у разі трігерів, справедливі і для вхідних сигналів регістрів. Наприклад, не повинна бути дуже малою тривалість сигналу С, а також не повинна бути дуже малою затримка між встановленням сигналу D і приходом позитивного фронту сигналу С. Інакше робота регістра може бути нестабільною або навіть неправильною.

Одне з основних вживань регістрів полягає в зберіганні необхідного коду протягом потрібного часу. Якщо для роботи решти частини схеми необхідно мати вхідний код, який можна легко змінювати, то для цього якраз підходить регістр.

На малюнку 24.3 показана типова схема включення регістра для зберігання коду і тимчасова діаграма його роботи. Код на вході регістра може змінюватися довільним чином, але в той момент, коли цей код приймає необхідне значення, на вхід С трігера подається синхросигнал (строб), який записує код в регістр. Цей код зберігатиметься в регістрі до приходу наступного строба. Причому важливо і те, що всі розряди вихідного коду регістра перемикатимуться одночасно навіть у тому випадку, коли розряди вхідного коду перемикаються не одночасно. Головне, щоб до приходу позитивного фронту строба (сигналу С) всі розряди вхідного коду прийняли потрібне, стійке значення.

Малюнок 24.3. Зберігання коду в паралельному регістрі.

Ще одне найважливіше вживання регістрів пов'язано із запам'ятовуванням декількох послідовних значень вхідного коду, що змінюється. Це дозволяє, наприклад, порівнювати попереднє значення коду з подальшим значенням цього ж коду або проводити арифметичні операції над декількома послідовними значеннями одного і того ж коду. Тобто регістр в даному випадку виступає як елемент лінії затримки, що береже в собі історію поведінки вхідного коду.

Регістри також широко використовуються для організації конвейєрної обробки, що дозволяє істотно підвищити тактову частоту роботи схеми. Прискорення при цьому досягається за рахунок розпаралелювання роботи декількох послідовно включених вузлів схеми.

Хай, наприклад, послідовність вхідних кодів, наступних з періодом Т, поступає на вхід ланцюжка з двох вузлів, що проводять обробку або перетворення цих кодів (малюнок 24.4). Вузли ці можуть бути комбінаційними мікросхемами (наприклад суматори) або складнішими пристроями, що включають мікросхеми лічильників або мікросхеми пам'яті. Головне полягає в тому, що вихідні сигнали цих вузлів виставляються не миттєво, а протягом якогось кінцевого часу, величина якого визначається внутрішньою будовою вузла. Хай затримка встановлення вихідного коду першого вузла дорівнює t1, а затримка встановлення вихідного коду другого вузла складає t2. Очевидно, що період проходження вхідних кодів Т не повинен бути менше ніж сума цих двох затримок:

T>t1+t2.

Інакше код на виході ланцюжка може ніколи не прийняти стійкого значення, оскільки перехідний процес попереднього такту буде змінятися перехідним процесом наступного такту. Тобто швидкодія вузлів накладає жорстке обмеження на тактову частоту.

Малюнок 24.4. Робота послідовного ланцюжка двох вузлів.

Проте можна обійти це обмеження, якщо скористатися принципом конвейєра, примусити вузли працювати не послідовно, а паралельно. Це досягається включенням між вузлами регістра, тактованого вхідним тактовим сигналом. Ще один регістр доцільно включити на вході другого вузла, що забезпечить тривалість стійкого коду на виході всього пристрою, рівну тривалості періоду тактового сигналу Т. В результаті обмеження на період тактового сигналу стає більш м'яким: Т не повинне бути менше максимальною з двох величин t1 і t2 з додаванням часу затримки регістра:

Т > max {t1,t2} + tRG.

Тобто до наступного фронту тактового сигналу повинен закінчити свою роботу найповільніший з вузлів, і тоді його вихідний код буде записаний в регістр правильно.

Малюнок 24.5. Конвейєрна обробка за допомогою регістрів.

Так само можна побудувати конвейєр на будь-яку кількість послідовно включених вузлів. Звичайно, в результаті введення конвейєра відбувається затримка виконання повної функції пристрою на число тактів, рівне числу введених регістрів. Проте у тому випадку, коли необхідно обробляти великі послідовності вхідних кодів, ця затримка спостерігається тільки один раз - на самому початку послідовності, а потім вже вона не має значення.

Регістри можуть також застосовуватися у складі обчислювачів, виконуючи функцію накопичувача результату обчислень. В даному випадку ми вже маємо справу з складнішою обробкою інформації, ніж у разі чисто комбінаційних схем. З кожним тактом в регістрі обновляється вміст, що є результатом математичної обробки вхідного коду і результату попереднього обчислення.

24.3. Регістри, що спрацьовують по рівню

Паралельні регістри, що спрацьовують по рівню стробуючого сигналу (або, як їх ще називають, регістри-защіпки, англійське Latch), можна розглядати як якийсь гібрид між буфером і регістром. Коли сигнал на стробуючому вході одиничний, такий регістр пропускає через себе вхідні інформаційні сигнали, а коли стробуючий сигнал стає рівний нулю, регістр переходить в режим зберігання останнього з пропущених значень вхідних сигналів.

Вживання таких регістрів сильно обмежено, хоча іноді вони досить зручні. В деяких схемах вони можуть успішно замінювати регістри, що спрацьовують по фронту, а в інших схемах їх вживання замість регістрів, що спрацьовують по фронту, неприпустимо.

В стандартних серіях мікросхем регістри, що спрацьовують по рівню, представлені набагато менше, ніж регістри, що спрацьовують по фронту. На малюнку 24.6 як приклади показано дві мікросхеми цього типу: 4-розрядного регістра ТМ7 і 8-розрядного регістра ИР22. Стробуючі входи С нерідко на схемах позначають Е (від англійського Enable - дозвіл) для того, щоб не плутати їх з тактовими входами D-триггеров.

Малюнок 24.6. Регістри, що спрацьовують по рівню.

Мікросхему ТМ7 (і близьку до неї ТМ5) часто називають набором трігерів, але її можна розглядати і як регістр. Мікросхема складається з чотирьох трігерів, стробуючі входи яких С сполучені попарно, тобто можна говорити про два двохрозрядні регістри-защіпки. Входи С1 і С2 мікросхеми управляють кожний двома розрядами даних. Всі трігери мають як прямі, так і інверсні виходи, що іноді дуже зручно. При одиниці на вході С вихідні сигнали повторюють вхідні, тобто регістр працює як звичайний буфер з прямими і інверсними виходами. При нулі на вході С на виході регістра постійно зберігається та вхідна інформація, яка була у момент приходу негативного фронту сигналу С. Але говорити, що регістр ТМ7 спрацьовує по негативному фронту сигналу С, невірно, оскільки інформація на виході міняється не тільки по цьому фронту, але і у момент зміни вхідних сигналів при С = 1.

Регістр ИР22 відрізняється від ТМ7 тим, що має виходи з трьома станами (і відповідно вхід дозволу всіх виходів -EZ) і тим, що всіма вісьма розрядами управляє один стробуючий сигнал С. Суть роботи від цього не змінюється. При одиниці на вході С регістр працює як буфер, а при нулі на вході С – зберігає ту інформацію, яка була на вході у момент негативного фронту сигналу С. Виходи у регістра ИР22 тільки прямі. Як і всі регістри з трьома станами виходу, регістр ИР22 має підвищену здатність навантаження.

Величини затримок трігерів, що спрацьовують по рівню, в 1,5-2 рази перевищують затримки D-триггеров. Для правильної роботи мікросхем позитивний імпульс на вході С не повинен бути дуже коротким, а затримка між зміною інформації на вході D і негативним фронтом сигналу С не повинна бути дуже малою. Інформація на вході D не повинна дуже швидко зніматися після негативного фронту сигналу С.

Основне вживання регістра, що спрацьовує по рівню стробуючого сигналу, полягає в запам'ятовуванні на якийсь заданий час вхідного коду, причому в решту часу вихідний код регістра повинен повторювати вхідний. Стробуючий сигнал С в цьому випадку повинен бути негативним на весь час запам'ятовування, і запам'ятовуватися буде вхідний код регістра у момент негативного (переднього) фронту сигналу С. Подібна функція буває, наприклад, необхідна при побудові пристроїв сполучення для комп'ютерів. Регістр, по суті, продовжує в часі необхідне значення вхідного коду, в решту часу працюючи як повторювач.

У ряді випадків регістри даного типу можуть успішно замінювати регістри, що спрацьовують по фронту. Наприклад, така заміна можлива у разі потреби запам'ятовування вхідного коду по сигналу С до моменту приходу наступного сигналу С.

Сигнал С в даному випадку повинен бути коротким позитивним імпульсом, причому він обов'язково повинен бути «вкладений » у вхідний код, що запам'ятовується, тобто починатися після початку (моменту встановлення) коду, а закінчуватися до кінця (моменту зняття) коду (це так званий вкладений цикл).

По передньому фронту сигналу С регістр перейде в режим пропускання вхідного коду, а по задньому - в режим його зберігання. Тому записуваний код на виході регістра з'явиться по позитивному фронту сигналу С, тобто точно так, як і у разі регістра, що спрацьовує по фронту.

Проте подібна заміна регістра, що спрацьовує по фронту, на регістр, що спрацьовує по рівню, можлива далеко не завжди. Деякі схеми у принципі не можуть працювати з регістром-защіпкою навіть при дуже короткому сигналі на вході С.

24.4. Зсувні регістри

Регістрами зсуву або зсувними регістрами (англійське Shift Register) є, як вже наголошувалося, послідовно сполучений ланцюжок трігерів. Основний режим їх роботи - це зсув розрядів коду, записаного в ці трігери, тобто по тактовому сигналу вміст кожного попереднього трігера переписується в наступний по порядку в ланцюжку трігер. Код, що зберігається в регістрі, з кожним тактом зсовується на один розряд у бік старших розрядів або убік молодших розрядів, що і дало назву регістрам даного типу.

З назвами напрямів зсуву в зсувних регістрах часто виникає плутанина. Зсув буває двох видів: управо (основний режим, який є у всіх зсувних регістрів) і вліво (цей режим є тільки у деяких, реверсивних зсувних регістрів). Назви ці відображають внутрішню структуру регістрів зсуву (малюнок 24.7.) і перезапис сигналів послідовно по ланцюжку трігерів. При цьому трігери, цілком природно, нумеруються зліва направо, наприклад, від 0 до 7 (або від 1 до 8) для 8-розрядних регістрів. В результаті зсув інформації регістром управо є зсувом у бік розрядів, що мають великі номери, а зсув інформації регістром вліво - це зсув у бік розрядів, що мають менші номери.

Малюнок 24.7. Напрям зсуву в зсувних регістрах.

Проте, як відомо, в будь-якому двійковому числі зліва розташовані старші розряди, а справа - старші розряди. Тому зсув двійкового числа управо буде зсувом убік молодших розрядів, а зсув вліво - зсувом у бік старших розрядів. Ця суперечність не чийсь злий намір, просто так склалося історично, і про це треба пам'ятати розробнику цифрової апаратури.

В стандартні серії цифрових мікросхем входить декілька типів зсувних регістрів, відмінних можливими режимами роботи, режимами запису, читання і зсуву, а також типом вихідних каскадів (2С або ЗС). Більшість регістрів зсуву має вісім розрядів. На малюнку 24.8. представлено для прикладу чотири типи мікросхем регістрів зсуву.

Регістр ИР8 - найбільш простій з регістрів зсуву. Він є 8-розрядною лінією затримки, тобто має тільки один інформаційний вхід, на який подається послідовна зсовувана інформація (точніше, два входи, з'єднані по функції 2І), і вісім паралельних виходів. Зсув у бік виходів із старшими номерами здійснюється по передньому фронту тактового сигналу С. Є також вхід скидання -R, по нульовому сигналу на якому всі виходи регістра скидаються в нуль. Таблиця істинності регістра ИР8 приведена нижче (таблиці 24.2).

Малюнок 24.8. Зсувні регістри.

Регістр ИР9 виконує функцію, зворотну регістру ИР8. Якщо ИР8 перетворить вхідну послідовну інформацію у вихідну паралельну, то регістр ИР9 перетворить вхідну паралельну інформацію у вихідну послідовну. Проте суть зсуву не міняється, просто в регістрі ИР9 всі внутрішні трігери мають виведені паралельні входи, і лише один, останній трігер має вихід (причому як прямий, так і інверсний). Запис вхідного коду в регістр проводиться по нульовому сигналу на вході -WR. Зсув здійснюється по позитивному фронту на одному з двох тактових входів С1 і С2, з'єднаних по функції 2АБО. Є також вхід розширення DR, сигнал з якого в режимі зсуву перезаписується в молодший розряд зсувного регістра.

Як і вся решта зсувних регістрів, регістри ИР8 і ИР9 допускають каскадування, тобто сумісне включення для збільшення розрядності. На малюнку 24.9. показано об'єднання трьох регістрів ИР8. В результаті об'єднання виходить 24-розрядний зсувний регістр. При цьому збільшення розрядності не приводить до збільшення затримки зсуву, оскільки тактові входи всіх регістрів, що використовуються, об'єднуються паралельно. У разі регістрів ИР8 вхідний послідовний код перетвориться в 24-розрядний вихідний паралельний код. У разі регістрів ИР9 вхідний 24-розрядний паралельний код перетвориться у вихідний послідовний код.

Регістр ИР13 поєднує в собі можливості регістрів ИР8 і ИР9. Він має як вісім входів для паралельного запису, так і відповідні їм вісім виходів паралельної інформації. Зсув здійснюється по позитивному фронту тактового сигналу С, причому зсув можливий як у бік старших розрядів (управо), так і убік молодших розрядів (вліво). Для нарощування розрядності у регістра ИР13 є послідовні інформаційні входи DR і DL, сигнали з яких вводяться відповідно в молодший і в старший розряди. Передбачено скидання всіх виходів регістра в нуль по нульовому сигналу на вході -R.

Малюнок 24.9. З'єднання регістрів ИР8 для збільшення розрядності.

Режим роботи регістра ІР 13 визначається двома управляючими входами SR і SL. При одиниці на вході SR і нулі на вході SL по фронту сигналу С відбувається зсув у бік старших розрядів. При нулі на вході SR і одиниці на вході SL по фронту сигналу С відбувається зсув убік молодших розрядів. При обох одиничних сигналах на входах SR і SL по фронту сигналу С відбувається паралельне завантаження інформації в регістр. Все це видно з таблиці істинності регістра ИР13(таблиця 24.3).

Відзначимо, що регістр ІР 13 застосовується помітно рідше, ніж більш прості регістри ИР8 і ИР9, оскільки задач, в яких були б потрібні всі можливості регістра ИР13 не так вже багато, а управління роботою регістра ІР 13 складне.

Нарешті, останній зсувний регістр, який ми розглянемо, це регістр ИР24. По своїх можливостях він близький до ИР13, проте його головною особливістю є двонаправлена паралельна шина даних. Тобто одні і ті ж виводи мікросхеми використовуються як для паралельного запису інформації в регістр, так і для паралельного читання інформації з регістра. При цьому двонаправлені виводи даних мають підвищену здатність навантаження. Це дозволяє легко сполучати регістр ИР24 з багаторозрядними мікросхемами пам'яті і з двонаправленими буферами. Тому застосовується даний регістр частіше, ніж ИР13.

Регістр ИР24 забезпечує зсув інформації в обох напрямах. Є входи розширення DR і DL, а також виходи розширення Q0 і Q7, що дозволяє легко нарощувати розрядність. Відмінність виходів Q0 і Q7 від нульового і сьомого розрядів даних полягає в тому, що Q0 і Q7 - однонаправлені, тобто в будь-якому режимі роботи видають інформацію з виходів внутрішніх трігерів молодшого і старшого розрядів. Тактується регістр позитивним фронтом сигналу С. Передбачено скидання регістра нульовим сигналом на вході -R.

Режим роботи мікросхеми визначається сигналами на управляючих входах SR і SL.

При одиничному сигналі на SR і нульовому сигналі на SL по позитивному фронту сигналу С відбувається зсув інформації управо (у бік розрядів з більшими номерами). Запис в розряд 0 проводиться при цьому з входу розширення DR.

При одиничному сигналі на SL і нульовому сигналі на SR по позитивному фронту сигналу С відбувається зсув інформації вліво (у бік розрядів з меншими номерами). Запис в розряд 7 проводиться при цьому з входу розширення DL.

При обох нулях на входах SR і SL регістр переходить в режим зберігання. У всіх цих випадках розряди даних працюють як вхід або як вихід залежно від сигналів -EZ.

При обох одиницях на входах SR і SL по позитивному фронту С в регістр записується паралельний код, причому розряди даних переходять в стан прийому незалежно від сигналів -EZ. Таблиця істинності регістра ИР24 приведена нижче

Об'єднуючи два регістри ИР24, легко одержати 16-розрядний зсувний регістр із збереженням всіх можливостей однієї мікросхеми. Так само можна об'єднувати і більшу кількість мікросхем.

Головне вживання всіх регістрів зсуву полягає в перетворенні паралельного коду в послідовний і навпаки. Таке перетворення використовується, наприклад, при передачі інформації на великі відстані (в інформаційних мережах), при записі інформації на магнітні носії, при роботі з телевізійними моніторами і з відеокамерами, а також в багатьох інших випадках.

Як приклад на малюнку 24.10. показана найпростіша схема передачі цифрової інформації в послідовному коді по двох лініях: інформаційною і синхронізуючою. Така передача дозволяє скоротити кількість сполучних дротів, а також спростити захист передаваних даних від дії зовнішніх електромагнітних перешкод, правда, ціною зниження швидкості передачі.

Малюнок 24.10. Послідовна передача інформації за допомогою регістрів зсуву.

На передаючому кінці (зліва на малюнку) за допомогою зсувного регістра ИР9 вхідний паралельний 8-розрядний код перетвориться в послідовність розрядів даних, що передаються з частотою тактового сигналу. На приймальному кінці (справа на малюнку) за допомогою зсувного регістра ИР8 ця послідовність розрядів даних знову перетвориться в паралельний код. Обидва регістри тактуються одним і тим же тактовим сигналом, який передається по лінії зв'язку паралельно з послідовністю даних. Для збільшення надійності передачі інформаційний сигнал додатково затримується щодо фронту тактового сигналу за допомогою ланцюжка з двох інвертувань.

Перший біт послідовного входу (з входу 7 регістра ИР9) починає передаватися з початком сигналу запису -Зап. Наступні розряди передаються з кожним наступним позитивним фронтом тактового сигналу С. Останнім передається сигнал з входу 0. В регістр ИР8 розряди послідовного коду записуються в тому ж самому порядку, в якому вони були в регістрі ИР9. Після закінчення передачі перший переданий сигнал даних опиниться в розряді 7 шини даних регістра ИР8, а останній переданий сигнал даних - в розряді 0.

Наступне використання зсувних регістрів полягає в організації всіляких ліній затримок, каскадів. За допомогою зсувних регістрів можна забезпечити затримку будь-якого вхідного сигналу на ціле число тактів. Правда, треба враховувати, що тривалість вхідного сигналу (і будь-якого його елемента) також передаватиметься по лінії затримки з точністю до одного такту. Такі лінії затримки можуть застосовуватися для порівняння декількох подальших тактів вхідного сигналу, для виконання арифметичних операцій з декількома тактами вхідного сигналу, для інших подібних цілей.(малюнок 24.11.)

Малюнок 24.11. Лінії затримки вхідного сигналу на зсувному регістрі

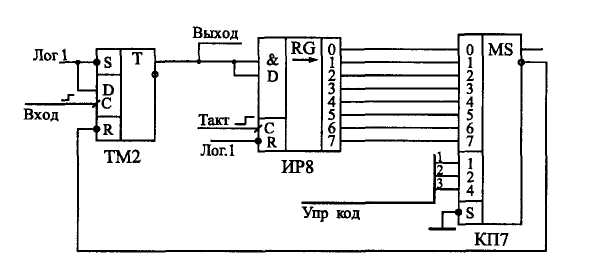

Зсувні регістри можуть також застосовуватися для формування імпульсів заданої тривалості, причому тривалість імпульсу може задаватися управляючим кодом, тобто бути програмно керованою. На малюнку 24.12. приведена можлива схема такого формувача.

В початковому стані (до приходу позитивного фронту вхідного сигналу) трігер скинений в нуль, на всіх виходах регістра зсуву нулі, на інверсному виході мультиплексора одиниця. На мультиплексор поданий управляючий код, що визначає тривалість вихідного сигналу. Під час вступу позитивного фронту вхідного сигналу трігер перекидається в одиницю (початок дії вихідного імпульсу), і цей одиничний сигнал починає послідовно зсовуватися регістром зсуву по кожному фронту тактового сигналу.

Малюнок 24.12. Формувач імпульсів з тривалістю, що задається управляючим кодом

Хай управляючий код рівний 5. Тоді в той момент, коли на виході 5 зсувного регістра з'явиться одиниця, вона буде передана на вихід мультиплексора КП7 з інверсією. При цьому нульовий сигнал на вході -R трігера скине трігер в нуль, що відповідає закінченню дії вихідного імпульсу.

Таким чином, тривалість вихідного сигналу визначатиметься управляючим кодом. Похибка установки цієї тривалості рівна одному періоду тактового сигналу і залежить від тимчасового зсуву між фронтом вхідного сигналу і фронтом найближчого до нього тактового імпульсу. Чим більше тривалість вихідного сигналу, тим менше відносна погрішність установки його точності. Наприклад, при керуючому коді 0 тривалість вихідного сигналу може бути від 0 до Т, де Т - період тактового сигналу. А при управляючому коді 7 тривалість вихідного сигналу буде від 7Т до 8Т. При цьому ми не враховуємо затримок трігера, зсувного регістра і мультиплексора.

Зсувні регістри можуть також використовуватися для множення і ділення двійкових чисел на 2П, де п - ціле число, більше нуля. Зсув двійкового числа управо (убік молодших розрядів) на один розряд рівносильний поділу на 2. Зсув двійкового числа вліво (у бік старших розрядів) на один розряд рівносильний множенню на 2. Для того, щоб зсувний регістр множив і ділив двійковий код, треба всього лише записати цей код в регістр і зсунути його потрібну кількість раз управо або вліво. Найбільш зручний для цього регістр ИР13. При цьому необхідно, щоб в розряди, що звільнилися, вводилися нулі, тобто на входи розширення DR і DL регістра потрібно подати нульові сигнали.

Нарешті, останнє вживання зсувного регістра - це генератор випадкової послідовності сигналів або випадкової послідовності кодів. Строго кажучи, послідовності будуть не повністю випадкові, а квазівипадкові, тобто періодично повторюватимуться, але період цей досить великий. Випадкові послідовності сигналів і кодів широко застосовуються в тестуючій апаратурі, в генераторах шуму, в логічних ігрових пристроях.

Задача полягає в тому, щоб вихідний сигнал або код міняв свій стан випадково (або майже випадково). Сигнал повинен випадково перемикатися з 0 в 1 і з 1 в 0, а код повинен випадково приймати значення з діапазону від 0 до (2 -1), де N - число розрядів коду (наприклад, від 0 до 255 при 8-розрядному коді). псевдовипадкові послідовності мають ту перевагу перед істинно випадковими, що вони передбачені і періодичні, але в цьому ж і їх недолік.